|

ę╗Ż®Ė┼╩÷

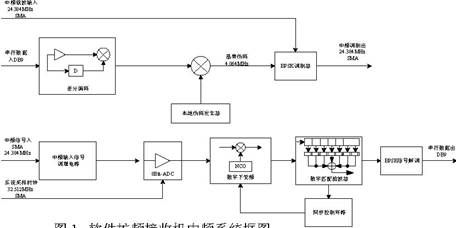

įōšnŅ}į┤ė┌▒Š▓®╩┐³c═©▀^═Ōģf║Žū„ßśī”čbéõ┐š▄ŖĄ─┐╣Ė╔ö_ļŖ┼_│÷┐┌ą═▀MąąĖ─įņįOėŗĄ─īŻĒŚšnŅ}Ż¼─┐ś╦×ķ╠ß╣®ę╗ĘN┐╔ŠÄ│╠┼õų├Ą─┐╣Ė╔ö_ļŖ┼_Ż¼─▄ē“Ė∙ō■ąĶę¬ī”«öŪ░╬ę┐š▄ŖčbéõĄ──│ą═│¼Č╠▓©┐╣Ė╔ö_ļŖ┼_▀Mąąąį─▄ųĖś╦Ą─┐sĘ┼┐žųŲŻ¼ęį▀mæ¬│÷┐┌ą═╠¢Ą─ąĶę¬ĪŻų„ę¬ā╚╚▌░³└©Įė╩šÖC║╦ą─╦ŃĘ©Ą─Ė─▀MŻ¼ī”öUŅl┤aĄ─┤aķL┐╔┼õų├Ż¼ęį╝░ī”æ¬▓╗═¼┤aķL║═┤aą“┴ąĄ─ŽÓĻPŲ„Ą─įOėŗ║═ģóöĄ┼õų├ĘĮ╩ĮĄ─įOėŗĪŻĮė╩šÖC×ķöĄūųųąŅl▄ø╝■Įė╩šÖCŻ¼┐╔į┌å╬Ų¼FPGA╔ŽīŹ¼F┴╦öĄūųųąŅlą┼╠¢ĮŌš{╦ŃĘ©ęį╝░öĄō■▌ö╚ļ▌ö│÷Įė┐┌Ą─╚½▓┐╣”─▄ĪŻ

Č■Ż®╣żū„įŁ└Ē

▄ø╝■öUŅlĮė╩šÖC░³║¼╔õŅlŪ░Č╦Ż¼Ņl┬╩║Ž│╔Ų„Ż¼öĄūųųąŅl─ŻēKęį╝░ļŖį┤─ŻēKŻ¼▌oų·š{įć─ŻēKĄ╚Ųõ╦¹═Ōć·ļŖ┬ĘĪŻ

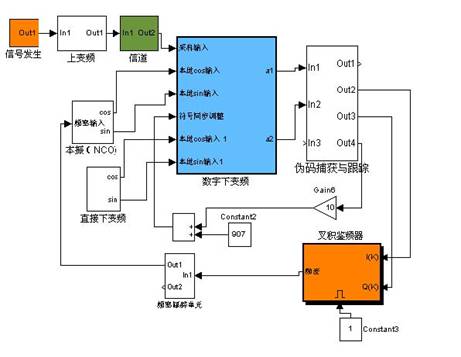

▒ŠšnŅ}║╦ą─▓┐Ęų×ķ┐╔ņ`╗Ņ┼õų├Ą─öĄūųųąŅlą┼╠¢╠Ä└Ē─ŻēKŻ¼īóė├ė┌╠µōQ¼FčbĄ─┐╣Ė╔ö_ļŖ┼_ųąŅl╠Ä└Ēå╬į¬Ż¼Č■š▀Įė┐┌Ą─ÖCąĄ║═ļŖŲ„╠žąįīó▒Ż│ųę╗ų┬ęįų¦│ųų▒Įė─ŻēK╠µōQĪŻŲõ╦¹─ŻēKų„ę¬ė├ė┌čą░lļAČ╬▀Mąąūįų„š{įć║═“×ūCĄ╚ė├═ŠĪŻ

╚²Ż®▄ø╝■öUŅl╩šÖC╠ž³c

1Ż® å╬ąŠŲ¼ųąŅlą┼╠¢╠Ä└Ēå╬į¬

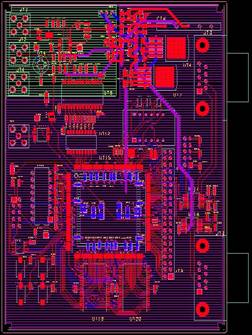

į┌å╬Ų¼FPGAŻ©Altera╣½╦ŠĄ─CycloneŽĄ┴ą EP1C12Ż®ųąīŹ¼F┴╦öĄūųųąŅlBPSK/DSą┼╠¢═Ļš¹Ą─░l╔õ║═Įė╩š▀^│╠ĪŻ

2Ż®▓╔ė├ĘųČ╬öĄūųŲź┼õ×V▓©Ų„īŹ¼Fą┼╠¢ĮŌöU

ų▒öUą┼╠¢ĮŌöU▓╔ė├ĘųČ╬╩ĮŲź┼õ×V▓©Ų„ą╬╩ĮĄ─ŽÓĻPŲ„Ż¼ūŅ┤¾┤aķL128Ż¼Ūę┤aķL┐╔ūāĪŻī”Ųź┼õ×V▓©Ų„Ą─ė▓╝■īŹ¼F▀Mąą┴╦┘Yį┤ā×╗»Ż¼┼õ║Žš█»B╩ĮĄ─ŽÓĻPŲ„ĮYśŗŻ¼š╝ė├Ą─ė▓╝■┘Yį┤▒╚ų▒ĮėīŹ¼FĘĮ╩Į┤¾┤¾£pąĪĪŻ

3Ż®╗∙ė┌SOPC╝╝ągĘĮ░ĖŻ¼┐╔öUš╣īŹ¼F▄ø╝■öUŅlĮė╩šÖC

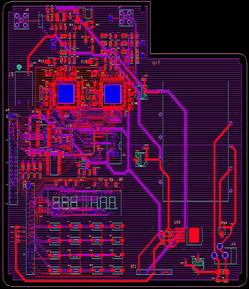

į┌FPGAųą╝»│╔AlteraĄ─▄ø║╦╠Ä└ĒŲ„Ż¼┼õ║ŽŲõ▄ø╝■ųĖ┴ŅČ©ųŲ╣”─▄║═Ųõ╦¹┐╔ė├IP┘Yį┤Ż¼śŗĮ©┴╦ę╗éĆ▄ø╝■öUŅlĮė╩šÖCĄ─ŲĮ┼_ĪŻ

4Ż®ōĒėą═Ļš¹Ą─╦ŃĘ©║═▄øė▓╝■┘Yį┤Ż¼▀mæ¬▓╗═¼æ¬ė├ąĶŪ¾ĪŻ

╗∙ė┌ĘųČ╬╩ĮŲź┼õ×V▓©Ų„Ą─ą┼╠¢ĮŌš{╦ŃĘ©┐╔ęįų¦│ųĖ▀äėæBą┼╠¢Ą─Įė╩šŻ¼╠ß╣®┴╦äėæBŚl╝■Ž┬¬Ü╠žĄ─¤o┐pŪąōQĄ─µiŅlŁh┬Ę┐žųŲ╦ŃĘ©Ż¼╩╣Ą├▌d▓©╗ųÅ═Ė³×ķ┐ņĮ▌ĪóŲĮĘĆĪŻ┤╦═ŌŻ¼▀ĆŠ▀éõ═Ļš¹Ą─MatlabĘ┬šµ─Żą═Ż¼Verilogė▓╝■Ę┬šµ─Żą═║═ęįFPGA░Õ×ķųąą─ė▓╝■£yįćŲĮ┼_Ż¼┐╔ū„×ķĄ┌╚²ĘĮė├üĒčą░löUŅl═©ą┼«aŲĘĄ─ģó┐╝ŲĮ┼_ĪŻ

łD1. ▄ø╝■öUŅlĮė╩šÖCųąŅlŽĄĮy┐“łD

╦─Ż®ų„ę¬╝╝ągųĖś╦

╗∙ĦöĄō■š{ųŲĘĮ╩ĮŻ║DBPSK\QPSK

╗∙ĦöĄō■é„▌ö╦┘┬╩Ż║32\64\128kb/s

ų▒öUöUŅl┤aŻ║128╬╗Ą─Mą“┴ąŻ©┤aą═┐╔▀xŻ®Ż╗

ų▒öUé╬┤a╦┘┬╩Ż║4.096Mb/s

╗∙Ħ│╔ą╬├}ø_Ż║ØLĮĄŽĄöĄ┐╔š{Ą─╔²ėÓŽę├}ø_Ż╗

ųąŅlŅl┬╩Ż║24.384MHzŻ©┐╔▀xŻ®Ż╗

ųąŅlą┼ŽóĦīÆŻ║┤¾ė┌8MHzŻ╗

ųąŅl▌ö╚ļą┼įļ▒╚Ż║0dB~-5dB

ČÓŲš└šŅlęŲŻ║▓╗ąĪė┌40KHzŻ╗

═¼▓ĮĢrķgŻ║▓╗┤¾ė┌50msŻ©é╬┤a▓Č½@Ģrķg×ķ1éĆĘ¹╠¢Ų┌Ż®

╬ÕŻ®æ¬ė├Ū░Š░

▒Š─ŻēK╩Ū┐╣Ė╔ö_ļŖ┼_Ą─║╦ą─╣”─▄─ŻēKŻ¼┐╔ūāķLČ╚Ą─öUŅl┤aķLī”æ¬ė┌┐╔ęį▓╗═¼╝ēäeĄ─┐╣Ė╔ö_═©ą┼─▄┴”Ż¼▀@ę╗╠ž³c╩╣įOéõ┐╔ęįĖ∙ō■æ¬ė├ŁhŠ│Ą─ę¬Ū¾Ż¼įOų├ŽÓæ¬ķLČ╚Ą─öUŅl┤a║═┤aą═Ż¼Č°¤oąĶĖ─äėļŖ┼_Ą─ė▓╝■▓┐ĘųŻ¼ūīę╗éĆą═╠¢Ą─ļŖ┼_┐╔ęį▀mæ¬ČÓĘN▓╗═¼ę¬Ū¾Ą─æ¬ė├ŁhŠ│Ą─ę¬Ū¾ĪŻ

öĄūųųąŅlą┼╠¢╠Ä└Ē─ŻēKĄ─┼õų├ņ`╗ŅąįŻ¼┐╔ęįÅVĘ║æ¬ė├ė┌ČÓĘN═╗░l╩ĮšZę¶ĪóöĄō■Ė▀äėæB¤oŠĆ═©ą┼ł÷║Žęį╝░GPSą┼╠¢Įė╩šÖCįOėŗĪŻ

|